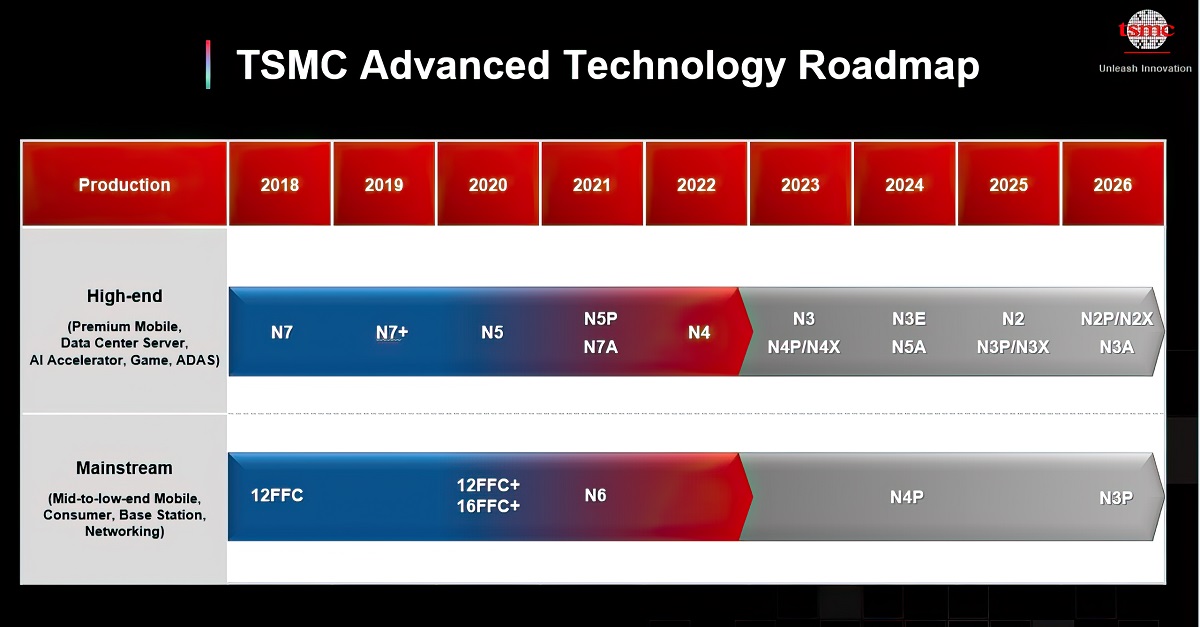

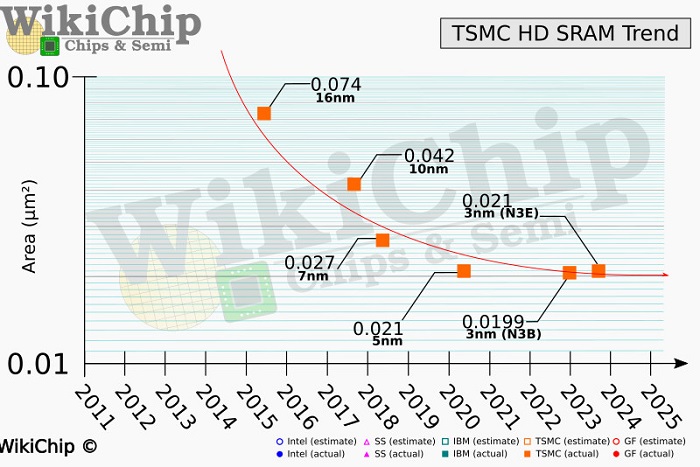

去年有报道称,SRAM单元在台积电3nm制程节点上,与5nm制程节点基本没有分别。这一消息也印证了过去的传言,即台积电(TSMC)在3nm制程节点遇到SRAM单元缩减放缓的问题,采用N3B和N5工艺的SRAM位单元大小分别为0.0199μm²和0.021μm²,仅缩小了约5%,而N3E工艺更糟糕,基本维持在0.021μm²,这意味着几乎没有缩减。

据报道,随着新一代2nm制程节点的到来,SRAM单元缩减问题似乎看到了曙光。与3nm制程节点不同,台积电在2nm制程节点将引入GAA晶体管架构,有望显著降低功耗,提高性能和晶体管密度,带来质的改变。台积电将在今年12月的IEDM会议上发表的一篇论文,提到了2nm制程节点将HD SRAM位单元尺寸缩小到约0.0175μm²。

这将是一个重大的突破,近年来SRAM单元的扩展已经变得相当困难,而通过N2工艺,台积电最终缩减了HD SRAM位单元尺寸,从而提高了SRAM密度。按照目前的情况来看,GAA晶体管架构似乎是HD SRAM位单元尺寸缩小的主要推动力。

要知道现代的CPU、GPU和SoC设计都非常依赖于SRAM密度,需要大容量缓存来有效地提升处理大批量数据的能力。从内存访问数据既消耗性能又耗电,因此充足的SRAM对于优化性能至关重要。展望未来,对高速缓存和SRAM的需求将持续增长,因此台积电在SRAM单元尺寸方面的成就显得非常重要。